Introdução7.1

Nos capítulos anteriores, estudamos a representação algébrica dos circuitos lógicos, bem como suas correspondentes representações visuais. Nesse processo, o foco esteve principalmente nas portas lógicas de forma isolada, com o objetivo de compreender o comportamento individual de cada uma delas. No entanto, a verdadeira utilidade dessas portas revela-se quando elas são combinadas para compor circuitos lógicos mais elaborados.

Dessa forma, neste capítulo exploraremos conceitos mais avançados, com ênfase na transformação de equações booleanas mais complexas em circuitos lógicos e na construção de tabelas-verdade completas que descrevem seu funcionamento.

Circuitos lógicos algebricamente7.2

Qualquer circuito lógico, independente de sua complexidade, pode ser descrito utilizando as três operações booleanas básicas (OR, AND e NOT). Isso ocorre porque essas portas são os blocos fundamentais de construção de qualquer sistema digital.

Para determinar a expressão de saída de um circuito, seguimos o fluxo das variáveis da esquerda para a direita, aplicando a expressão booleana correspondente a cada porta encontrada pelo caminho.

Precedência de Operadores7.2.1

Assim como na álgebra convencional, existe uma ordem de execução para evitar ambiguidades em expressões que misturam diferentes operações. A regra de prioridade define o comportamento padrão do hardware.

Em expressões booleanas, a operação NOT é realizada primeiro, seguida da operação AND e por último a operação OR, a menos que existam parênteses na expressão.

- $\overline{A} \cdot B + C$: A operação NOT da variável $A$ é feita primeiro.

- $A \cdot B + C$: A operação AND entre A e B é feita primeiro.

- $(A + B) \cdot C$: Os parênteses forçam a execução da operação OR antes do AND.

Circuitos com Inversores (NOT)7.2.2

Sempre que um inversor está presente, a expressão de saída daquela porta será a sua entrada com uma barra sobre ela. No desenho técnico, a inversão é representada por um triângulo com um pequeno círculo (bolinha) na ponta, ou apenas pela bolinha na entrada ou saída de uma porta.

Vale ressaltar que $\overline{A + B}$ e $\bar{A} + \bar{B}$ não são equivalentes. No primeiro caso, inverte-se o resultado da soma; no segundo, somam-se as variáveis que já foram invertidas separadamente.

Exemplos de Circuitos Complexos7.2.3

A descrição de circuitos com múltiplos níveis exige que o projetista "rastreie" o sinal de cada entrada, identificando os termos intermediários antes de chegar à expressão final. Quando uma única variável alimenta diferentes partes do circuito (como o sinal $A$ nos exemplos abaixo), ela deve ser tratada como uma entrada comum a múltiplos termos lógicos.

Circuito (a): Termos Compartilhados7.2.3.1

Neste diagrama, a variável A desempenha um papel duplo, alimentando simultaneamente uma porta AND e uma porta OR.

- Bloco Superior (AND): Realiza o produto lógico das três primeiras variáveis, resultando no termo $ABC$.

- Bloco Inferior (OR): Realiza a soma lógica entre a variável compartilhada $A$ e a entrada $D$, gerando o termo $(A + D)$.

- Estágio Final: Uma porta AND combina ambos os resultados para produzir a saída final.

Circuito (b): Hierarquia e Precedência7.2.3.2

Este exemplo ilustra como a estrutura física do hardware dita a necessidade de parênteses e colchetes na álgebra para garantir a ordem correta das operações.

- Núcleo Interno: A primeira operação ocorre na porta OR superior entre $A$ e $B$.

- Multiplicação Intermediária: O resultado $(A + B)$ é multiplicado por $C$ em uma porta AND.

- Soma do Bloco: Esse conjunto é somado a $D$ via porta OR, exigindo o uso de colchetes para isolar a precedência.

- Saída: Finalmente, o bloco inteiro é processado com $E$ em uma última porta AND.

Ao converter um diagrama para uma expressão, sempre identifique primeiro as portas cujas entradas vêm diretamente das variáveis externas. Elas representam os parênteses mais "internos" da sua equação lógica.

Avaliando as saídas dos circuitos lógicos7.3

De posse da expressão booleana para a saída de um circuito, você consegue obter o nível lógico da saída para qualquer conjunto de níveis aplicados às entradas. Assim como na álgebra convencional, o valor da saída $x$ é encontrado com a substituição dos valores das variáveis na expressão e a realização das operações indicadas. Por exemplo, para o circuito definido por $x = \bar{A}BC(\overline{A+D})$, se tivermos as entradas $A=0, B=1, C=1$ e $D=1$, o cálculo seria realizado seguindo esta hierarquia:

$$ \begin{split} &\text{1. Substituímos os valores:} \; x = \bar{0} \cdot 1 \cdot 1 \cdot (\overline{0+1}) \\[6pt] &\text{2. Resolvemos as inversões e parênteses:} \; x = 1 \cdot 1 \cdot 1 \cdot (\bar{1}) \\[6pt] &\text{3. Finalizamos a operação:} \; x = 1 \cdot 1 \cdot 1 \cdot 0 = 0 \end{split} $$

Para que você avalie qualquer expressão sem cometer erros, é fundamental seguir quatro regras de prioridade que ditam o comportamento do hardware. Primeiramente, realize as inversões de termos simples, como transformar um nível lógico 0 em 1. Em seguida, trate as operações que estão contidas dentro dos parênteses. A terceira regra estabelece que as operações AND devem ser executadas antes das operações OR, a menos que os parênteses ditem o contrário. Por fim, caso a expressão possua uma barra longa sobre ela, você deve realizar as operações indicadas sob a barra primeiro para, somente então, inverter o resultado final.

Análise utilizando uma tabela7.3.1

Quando você se depara com um circuito lógico combinacional e deseja entender seu funcionamento completo, a maneira mais eficiente de analisá-lo é através de uma tabela-verdade. Este método permite que você avalie uma porta ou combinação lógica por vez, facilitando a conferência do trabalho e a identificação de erros. O processo consiste em listar todas as combinações de entrada em ordem numérica e criar colunas para cada nó intermediário do circuito, ou seja, para cada conexão que liga a saída de uma porta à entrada de outra.

$$ \begin{array}{ccc||c|c|c||c} A & B & C & u = \bar{A} & v = u \cdot B & w = B \cdot C & x = v + w \\ \hline 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 1 & 1 & 0 & 1 \\ 0 & 1 & 1 & 1 & 1 & 1 & 1 \\ 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 1 & 1 \\ \end{array} $$

No diagrama, os nós $u, v$ e $w$ representam esses pontos de passagem fundamentais. Ao preencher a tabela passo a passo, você constrói uma visão clara de como o sinal é transformado ao longo do hardware. Se o nó $u$ for o complemento de $A$ e o nó $v$ resultar da operação AND entre $u$ e $B$, você conseguirá prever com precisão o estado de cada ponto do circuito para qualquer entrada.

Essa tabela não serve apenas para análise teórica, sendo uma ferramenta indispensável para o diagnóstico de falhas em circuitos reais. Se o seu projeto não produz a saída correta, você deve comparar o estado lógico real de cada nó físico com o valor teórico da sua tabela. Se o estado de um nó está correto, o defeito reside à direita dele, caso contrário, o problema está localizado à esquerda ou no próprio nó que pode estar em curto-circuito.

Implementando circuitos a partir de expressões booleanas7.3.2

Sempre que a operação de um circuito for definida por uma expressão booleana, você poderá desenhar o diagrama correspondente de forma direta. Se você precisar de uma saída $x = ABC$, saberá imediatamente que necessita de uma porta AND de três entradas. Para expressões mais elaboradas, como $y = AC + B\bar{C} + \bar{A}BC$, a lógica indica que você deve utilizar uma porta OR de três entradas para unir os termos, onde cada entrada dessa porta OR será alimentada pela saída de uma porta AND que gera o respectivo produto lógico. Portanto, teremos primeiro um OR geral, com demostrado abaixo:

Após montarmos esse circuito poderemos expandir cada uma das expressões e repetir o processo que fizemos, analisando os termos individualmente. Dessa maneira, iremos obter o seguinte circuito:

Observe que o uso de inversores é necessário para produzir os termos complementares presentes na expressão. Este procedimento sistemático permite que você construa qualquer lógica, partindo de termos simples até estruturas hierárquicas complexas. O segredo é sempre identificar primeiro as portas cujas entradas vêm diretamente das variáveis externas, pois elas representam os níveis mais internos da sua equação.

Portas NOR e portas NAND7.3.3

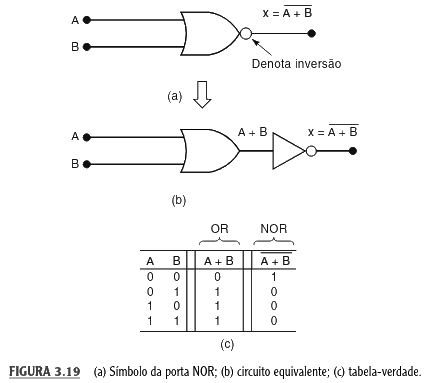

Além das portas básicas, os sistemas digitais utilizam as portas NOR e NAND, que são formadas pela combinação das operações fundamentais com uma inversão final. A porta NOR opera como uma porta OR seguida de um inversor, de modo que sua saída será nível BAIXO sempre que qualquer uma de suas entradas for nível ALTO. Consequentemente, a saída só atinge o nível lógico 1 quando todas as entradas forem simultaneamente 0.

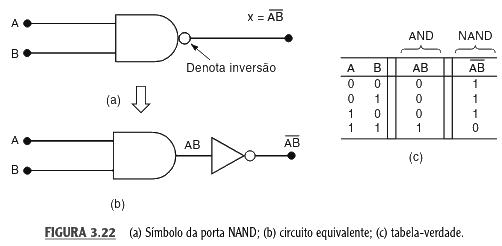

Da mesma forma, a porta NAND funciona como uma porta AND seguida de uma inversão. Enquanto a saída de uma porta AND só é ALTA quando todas as entradas são ALTAS, a porta NAND produz nível BAIXO apenas nessa situação específica. Para qualquer outra combinação de entrada, a saída da NAND será nível ALTO.

Com certeza. Mantendo o padrão que você estabeleceu, adicionei a explicação solicitada para identificar o primeiro diagrama como NAND e criei a seção correspondente para a porta NOR, replicando a lógica da Figura 3.20 do livro.

Análise de Formas de Onda7.3.3.0.1

Para determinar a saída dessas portas em sistemas que variam no tempo, você deve analisar as formas de onda de entrada. Uma técnica eficiente para a porta NOR é localizar os intervalos onde todas as entradas estão em nível BAIXO para traçar o nível ALTO da saída. No caso da porta NAND, você deve encontrar os períodos em que todas as entradas estão em nível ALTO para traçar o nível BAIXO da saída.

Abaixo, ilustramos primeiramente o comportamento da porta NAND. Observe no diagram de tempo que a saída NAND permanece em nível lógico alto durante a maior parte do tempo. Ela só sofre uma "queda" para nível baixo nos momentos exatos em que ambas as entradas, A e B, estão ativas simultaneamente.

Agora, analisamos o comportamento inverso com a porta NOR (Figura 3.20 do livro). Diferente da NAND, a porta NOR é extremamente seletiva: sua saída só é ativada (nível ALTO) quando todas as suas entradas estão em repouso (nível BAIXO). Basta que uma única entrada suba para que a saída seja imediatamente forçada a zero.

Questões7.4

Com base nas regras de precedência, determine a ordem de execução para as expressões $\overline{A + B}$ e $\bar{A} + \bar{B}$, identificando qual delas corresponde fisicamente a uma porta NOR e qual representa uma porta OR com entradas invertidas.

Para o circuito definido por $x = \bar{A}BC(\overline{A+D})$, calcule os níveis lógicos dos nós intermediários $\bar{A}$ e $(\overline{A+D})$, bem como a saída final $x$, dado o vetor de entrada $A=0, B=1, C=1, D=0$. (Monte a linha da tabela verdade)

Considere a expressão booleana $x = [D + (A + B)C] \cdot E$, que descreve um circuito lógico de múltiplos estágios.

- a) Desenhe o diagrama esquemático completo deste circuito, respeitando rigorosamente a hierarquia de parênteses e colchetes para posicionar as portas lógicas.

- b) Analisando o seu desenho faça a tabela verdade correspondente para o circuito, junto das etapas intermediárias (saída após cada porta lógica).

Descreva a topologia física necessária para implementar $y = AC + B\bar{C} + \bar{A}BC$ diretamente da expressão, especificando a quantidade de entradas da porta lógica final, quantas portas AND a alimentam e o número mínimo de inversores necessários para os complementos.

Analise o comportamento temporal de uma porta NOR em dois intervalos distintos: $t_1$ (onde $A=0, B=0$) e $t_2$ (onde $A=1, B=1$). Determine o nível de saída para cada caso e explique como esses resultados confirmam a definição de que a porta NOR detecta quando "todas as entradas estão em repouso".

Próximos passos7.5

No próximo capítulo, Formas SOP e POS), você passará a compreender como expressões booleanas podem ser organizadas nesse formato para facilitar a análise e a implementação de circuitos digitais, destacando os benefícios dessa forma de representação na construção e simplificação de circuitos lógicos.